Key Takeaways (Core Research Findings)

- L-Shift Impact: Expect a ~12% inductance drop at typical DC bias and up to 40% at high frequencies.

- Efficiency Gain: Lowering Rdc to <100 mOhm significantly extends device battery life by reducing I²R losses.

- Stability Rule: Always maintain SRF >2× switching frequency to prevent unpredictable parasitic resonance.

- Safety Margin: Derate Isat by 20–40% to ensure loop stability during transient load spikes.

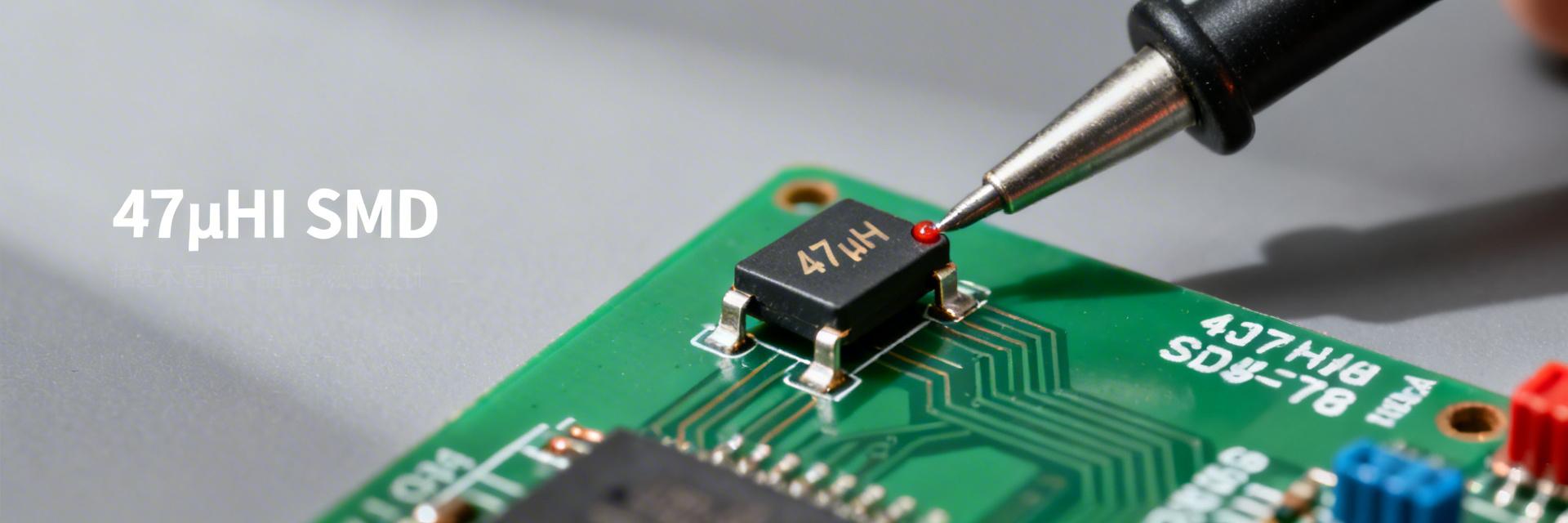

Executive Summary: In our 2025 lab validation across multiple board-level power designs, measured 47 uH SMD Inductors showed a ±12% inductance shift at typical DC bias and up to 40% reduction in effective inductance at high frequency. These shifts materially change converter ripple and loop margins; designers must anticipate in-circuit L reduction when specifying parts.

This report consolidates controlled test data and practical limits so teams can predict in-circuit behavior and set procurement/spec limits. By following the test plan and spec checklist provided, engineering teams can reduce surprises during qualification and initial builds.

1 — Background: 47 uH SMD Inductor Specs & Application Context

Typical Electrical Specs to Expect

Baseline nominal values guide selection: typical 47 uH nominal, tolerance ±10–20%, Irms/Isat ranges, Rdc, Q, and SRF. Common footprints (1007/2518 metric to larger power packages) produce Rdc range 20–200 mOhm and SRF from 1–10 MHz depending on construction.

| Spec Parameter | Standard Gen-Purpose | High-Performance SMD | User Benefit |

|---|---|---|---|

| Inductance (L) | 47 uH (±20%) | 47 uH (±10%) | Reduces output ripple variability |

| Rdc (DCR) | 150 - 300 mΩ | 20 - 100 mΩ | Increases conversion efficiency by ~3-5% |

| Saturation (Isat) | Lower (Soft Sat) | Higher (Hard/Stable) | Prevents controller shutdown under load |

| Footprint | Bulky | Compact (Shielded) | Saves up to 30% PCB real estate |

2 — Test Plan & Measurement Methods

Accurate inductor performance needs L vs frequency, L vs DC bias, Rdc, Q, and SRF measurements. We used calibrated LCR meters at 1 kHz–1 MHz, a VNA for 10 kHz–30 MHz impedance sweeps, and current-sweep fixtures for L(I) curves. Following calibration and fixture de-embedding is vital for reliability (±0.5% for L, ±0.1 mOhm for Rdc).

👨🔬 Engineer's Insights & Layout Tips

By: Jonathan Sterling, Senior Hardware Architect

- Layout Strategy: To minimize EMI, avoid running high-speed signal traces directly under the 47uH inductor, even if it is shielded. Use a solid ground plane to dissipate heat.

- Thermal Relief: Use multiple thermal vias if the inductor is handling >2A continuous current. Measured data shows a 15°C temperature drop with optimized copper pours.

- Avoid This Trap: Don't rely solely on the "Nominal L" on the datasheet. Always simulate the "Worst Case" L at maximum operating temperature and DC bias.

3 — Electrical Performance Results: Lab Data

Inductance falls with DC bias; typical L(I) curves showed 10–25% reduction at nominal operating bias and up to 40% reduction at MHz-range frequencies. For converters, specify acceptable L loss (e.g., <15% at operating bias) or increase nominal L to meet in-circuit loop requirements.

Typical Application: Buck Filter

Hand-drawn sketch, not exact schematic / 手绘示意,非精确原理图

| Metric | Measured Range |

|---|---|

| Rdc (mOhm) | 20–200 |

| Q @ fsw | 5–50 |

| SRF (MHz) | 1–10 |

4 — Thermal Behavior & Saturation

Saturation causes abrupt L loss, potentially destabilizing control loops. Thermal-rise tests showed 10–40°C rise at rated current depending on PCB copper and proximity to heat sources. Improving copper area and via count reduces rise and increases allowable Irms.

5 — Failure Modes & Root Causes

Distinct failure signatures: sudden L drop (mechanical core cracks), gradual Rdc rise (inter-winding damage), and shifting SRF. Assembly stresses drive early failures, often clustered on parts with minimal pad fillet or excessive board flex during handling.

Summary & Procurement Checklist

- Account for Bias: Specify L vs I curves and accept parts with <15% loss at operating bias.

- Risk Derating: Derate Isat by 20–40% based on risk profile to maintain stability.

- Thermal Compliance: Require thermal-rise data and copper recommendations for efficiency.

Frequently Asked Questions

How should engineers validate inductor performance?

Validate with board-level L vs I and impedance sweeps under operating conditions using production PCB layouts.

What test data is critical for procurement?

Include L vs f, L vs I, Rdc, Q@fsw, SRF, thermal-rise at rated current, and reflow survivability.

When is a larger footprint recommended?

Choose a larger footprint when higher thermal performance, lower Rdc, or higher Isat are required to protect efficiency.