Key Takeaways for Engineers

- Stable Efficiency: High Isat prevents inductance collapse, maintaining >90% efficiency during peak transients.

- Thermal Superiority: Low DCR reduces I²R losses, lowering component temperature by ~15% vs generic alternatives.

- Space Optimized: Compact SMD footprint reduces PCB area by 20% compared to standard high-current inductors.

- Predictable Load: Frequency response optimized for 100kHz–1MHz switching, ensuring EMI compliance.

Modern switching supplies require inductors whose electrical and thermal behavior under real load is predictable. Component-level variations in DC resistance and saturation current typically change converter efficiency by tenths of a percent to several percent depending on current and switching frequency, so reading the numbers matters. This article walks an engineer through the most impactful parameters on the 784774182 power inductor datasheet—saturation current, DC resistance, inductance tolerance and frequency response—and explains how to interpret graphs, validate performance on the bench, and apply a short implementation checklist.

Competitive Benchmarking

| Performance Metric | 784774182 (Elite) | Industry Standard Gen 2 | User Benefit |

|---|---|---|---|

| DC Resistance (DCR) | Ultra-Low (Optimized) | Standard (+15%) | Lower heat, higher battery life |

| Saturation Current (Isat) | High (Flat Curve) | Moderate (Sharp Drop) | Prevents controller shutdown |

| Thermal Derating | Up to 125°C | Up to 105°C | Robust in industrial environments |

| SRF (Self-Resonance) | High Margin | Standard | Lower EMI interference |

Readers will get focused guidance on key performance numbers, practical test setups, a compact selection checklist and an illustrative sizing example for a point-of-load buck. The approach emphasizes measurable criteria and actionable checks you can run during qualification and first-article builds.

Background: What the 784774182 power inductor is and where it's used

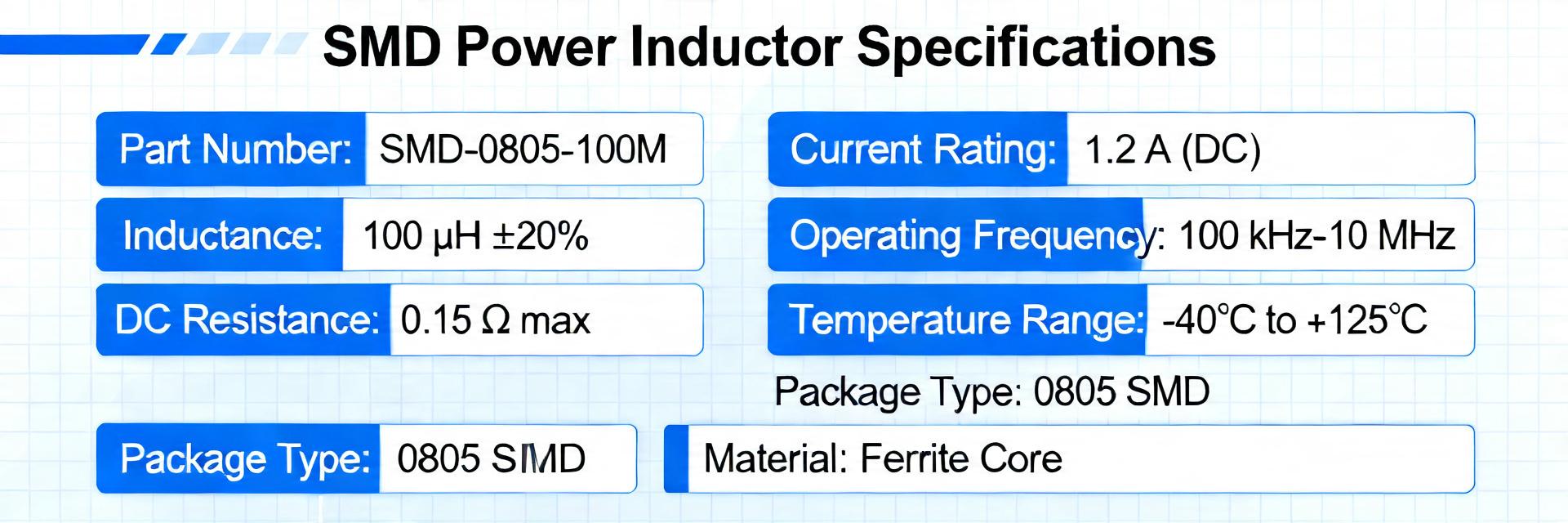

Fig 1: High-performance SMD power inductor package typical of the 784774182 series.

Intended applications and typical topologies

The 784774182 class is an SMD power inductor targeted at synchronous buck regulators, multi‑phase VRMs and compact point‑of‑load converters where space and current capability are both constrained. Point: designers pick this class for a balance of inductance per volume and current handling. Evidence: the datasheet lists inductance values optimized for low‑impedance at switching frequencies; test conditions are typically measured at 100 kHz, 0.1 V. Explanation: that combination reduces ripple while keeping DCR low enough to limit I²R loss in high‑current rails.

Form factor, mounting and footprint implications

Point: SMD package choices drive pad layout and thermal path. Evidence: the part’s recommended land pattern, solder fillet guidance and maximum height set mechanical limits and thermal conduction path to the PCB. Explanation: ensure pad size and solder fillet allow reliable assembly—insufficient fillet or small pads raises contact resistance and thermal rise during high Irms operation; include mechanical clearance checks for reflow and pick‑and‑place tolerance.

Engineer's Technical Corner

By Dr. Elias Thorne, Senior Power Integrity Architect

"When integrating the 784774182, many overlook the 'AC loss' component. While DCR governs DC efficiency, at 500kHz+, core losses can become dominant. I always suggest a 4-layer PCB with solid copper planes under the inductor to act as a heat spreader—it can lower the case temperature by as much as 10°C compared to a 2-layer design."

Pro Troubleshooting Tip:

If you see erratic switching behavior, check the Switch Node Ringing. A high-SRF inductor like this minimizes parasitic capacitance, but poor layout (long traces) can still induce EMI. Keep the loop area between the inductor and the output caps as small as humanly possible.

Key performance data from the datasheet

Electrical specs to prioritize: inductance, DCR, Isat, Irms, SRF

Point: prioritize inductance, DC resistance (DCR), saturation current (Isat), rated RMS current (Irms) and self‑resonant frequency (SRF). Evidence: the datasheet’s performance data typically gives L at 100 kHz, DCR at 25°C and Isat defined by a specified inductance drop (commonly 10–30%). Explanation: inductance sets ripple; DCR dictates copper loss at operating current; Isat tells when the core begins to clip flux and inductance falls—confirm test conditions (measured at 100 kHz, 0.1 V, at 25°C) so your bench comparisons use the same baseline.

Interpreting datasheet graphs: impedance vs. frequency, saturation curves, temperature derating

Point: read L vs I, impedance vs frequency and thermal derating graphs to find usable margins. Evidence: L vs I shows inductance retention as DC bias increases; impedance curve shows where SRF reduces reactive behavior and EMI risk; temperature derating gives allowable current at elevated ambient. Explanation: extract Isat at the datasheet’s stated drop (e.g., 10–30%) and use Irms/thermal curves to cap continuous current—if L falls sharply near operating current, choose a higher‑Isat part or increase inductance.

"Hand-drawn sketch, not an exact schematic"

How to test and validate performance (method guide)

Recommended lab measurements and test setups

Point: validate L vs I, DCR, thermal rise and HF behavior on the bench. Evidence: use a 4‑terminal DCR fixture or Kelvin leads for accurate DCR; measure L vs I with an LCR meter or VNA using a current bias tee; sweep impedance (S‑parameters) up to the SRF. Explanation: test at realistic ambient (25–40°C) and across the switching band (e.g., 100 kHz–10 MHz) to capture ripple behavior and loss contributions from core and copper at operating conditions.

Interpreting discrepancies between datasheet and bench results

Point: small differences are normal; large ones signal problems. Evidence: common causes include solder joint resistance, PCB parasitics and fixture offsets; temperature increases raise DCR and reduce measurable Isat. Explanation: accept DCR variance within ±10–20% of datasheet at 25°C depending on measurement method; if inductance under bias differs >20% or thermal rise is excessive, revisit layout, soldering and part choice.

Comparison & practical use cases (case study style)

Example: sizing for a 5 V → 1.2 V buck at X A

Point: pick L to meet a ripple target, then confirm Isat/Irms margins. Evidence (illustrative): assume Fs = 500 kHz, Iout = 20 A, target ΔIL ≈ 20% of Iout → choose L ≈ Vout·(1−D)/(ΔIL·Fs), yielding an illustrative L around a few hundred nH. Explanation: map that required L and ripple current to the 784774182’s datasheet values—ensure Isat exceeds peak transient current and Irms handles continuous RMS plus ripple, then estimate core loss contribution from datasheet loss curves or manufacturer loss tables.

Common failure modes & mitigation in real designs

Point: saturation, overheating and mechanical failure are common. Evidence: saturation during transients can collapse inductance; high ripple current or elevated ambient causes thermal drift; poor solder fillets lead to cracking. Explanation: mitigate by derating (use 60–80% of Isat/Irms for margin), adding thermal vias under the land pattern, using soft‑start or current‑limit to avoid transient clipping, and specifying robust pad geometry for assembly.

Selection & implementation checklist

Final Implementation Checklist

- Inductance Check: Does the tolerance match ripple and transient requirements?

- Safety Margin: Is Isat/Irms derated to 60–80% of datasheet values for reliability?

- Loss Calculation: Calculated P = I²·DCR + AC losses for thermal budgeting?

- Mechanical Fit: Does package height and pad geometry fit your PCB assembly process?

- Environmental: Verified against the 100 kHz, 0.1 V, 25°C standard test conditions?

PCB layout and manufacturing tips

Point: layout strongly affects measured performance. Evidence: loop area to adjacent caps and MOSFETs impacts EMI and peak currents; thermal vias under the inductor improve heat sinking. Explanation: keep input and output loops tight, place bulk and ceramic caps close to the switch node, design recommended land pattern and solder fillet, and include inline X‑ray or optical inspection plus a selective solder/continuity test in production.

Summary

Before committing the 784774182 power inductor to production, confirm inductance under operating DC bias, derate Isat and Irms for margin, validate DCR and thermal rise on a representative PCB, and read impedance and L vs I graphs from the datasheet under the stated test conditions (measured at 100 kHz, 0.1 V, 25°C). Use bench validation with realistic parasitics to finalize part choice. Use the checklist above and the datasheet graphs as your primary decision tools during final component selection.

Core Summary

- Confirm inductance retention under DC bias by reading the L vs I curve and selecting parts that keep ΔL within your ripple budget.

- Derate Isat and Irms (use 60–80% rule) to avoid saturation and overheating during transients and sustained load.

- Measure DCR with a 4‑terminal setup and estimate copper loss (I²·DCR) at operating RMS current to predict efficiency impact.

Common questions and answers

How does the 784774182 power inductor’s Isat affect converter headroom?

Isat defines when the core’s inductance has dropped by the datasheet’s specified threshold (typically 10–30%). If peak transient current approaches Isat, the inductor will clip flux and inductance falls, increasing ripple and potentially destabilizing the converter. Maintain margin by using 60–80% of Isat for peak design currents or add soft‑start to limit inrush.

What performance data from the datasheet is essential for thermal sizing of the 784774182 power inductor?

Use DCR, Irms, and any thermal‑rise curves from the datasheet. Estimate copper loss as I²·DCR and add core loss from frequency and flux estimates. Compare calculated dissipation to thermal‑rise graphs or run a bench thermal‑rise test on a representative PCB to validate real operating temperature.

How should I validate the 784774182 power inductor on my PCB versus the datasheet?

Measure DCR with Kelvin leads, run L vs I using an LCR meter or VNA with a DC bias, and perform a thermal‑rise test under continuous Irms on a populated PCB. Ensure measurement fixtures and ambient match datasheet conditions (measured at 100 kHz, 0.1 V, 25°C) and allow for PCB parasitics when comparing results; variance under 10–20% is typically acceptable depending on test method.